Advertisement

Grab your lab coat. Let's get started

Welcome!

Welcome!

Create an account below to get 6 C&EN articles per month, receive newsletters and more - all free.

It seems this is your first time logging in online. Please enter the following information to continue.

As an ACS member you automatically get access to this site. All we need is few more details to create your reading experience.

Not you? Sign in with a different account.

Not you? Sign in with a different account.

ERROR 1

ERROR 1

ERROR 2

ERROR 2

ERROR 2

ERROR 2

ERROR 2

Password and Confirm password must match.

If you have an ACS member number, please enter it here so we can link this account to your membership. (optional)

ERROR 2

ACS values your privacy. By submitting your information, you are gaining access to C&EN and subscribing to our weekly newsletter. We use the information you provide to make your reading experience better, and we will never sell your data to third party members.

Electronic Materials

Dipping technique makes high-performance carbon nanotube circuits

Method produces array of aligned, semiconducting carbon nanotubes for next-gen computer chips

by Neil Savage, special to C&EN

May 21, 2020

The ability to shrink silicon circuits in order to cram more of them onto chips and make ever higher performing computers, phones, and other gadgets is rapidly approaching its physical limit. Supplementing or replacing the silicon with carbon nanotubes could allow computing power to keep growing, but the tubes are tiny, tricky things to work with. Now a team in China has developed a method to collect the best carbon nanotubes and line them up in a way that will let them build new types of chips (Science, 2020, DOI: 10.1126/science.aba5980).

Carbon nanotubes are essentially sheets of graphene—single-layer collections of carbon atoms—rolled into a cylinder. Like graphene, they allow electrons to fly through them unimpeded, but like silicon they can be semiconductors, turning electron flow on and off in response to a change in voltage. Individual carbon nanotubes can be made into transistors, but it’s much easier to make them from groups of aligned tubes. The challenge is in the consistency of the materials. Some carbon nanotubes turn out metallic, so the electron flow won’t easily turn off. And to make a good transistor, they need to be packed densely enough to carry sufficient current.

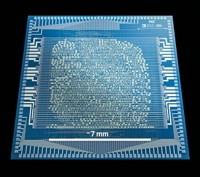

The method developed by Zhiyong Zhang and Lian-Mao Peng at Peking University’s Frontiers Science Center for Nano-optoelectronics sorts the nanotubes so that no more than one in a million is metallic, and aligns them on a silicon wafer at a density of between 100 and 200 per micrometer, up from the 47 achieved by previous researchers. The team demonstrated the feasibility of their method by using it to build a carbon-nanotube-based field-effect transistor that outperformed a similar device built of silicon.

They started with commercially available carbon nanotubes, and placed them in a toluene solvent to which they added the polymer poly[9-(1-octylonoyl)-9H-carbazole-2,7-diyl (PCz). The PCz wrapped around the individual nanotubes, which were then placed into a centrifuge that sorted the wrapped nanotubes. Repeating the process twice more further sorted them, to the point where 99.9999% of the nanotubes were semiconducting, an improvement over the 99.99% achieved by previous methods. They researchers say it should be possible to improve the selection of the nanotubes even more by repeating the process more times.

Next, they dipped a 10-cm silicon wafer into the solution of purified nanotubes and added a small amount of 2-butene-1,4-diol. The butene diol formed a thin layer that surrounded the wafer. Nanotubes floating in the solution bumped into the butene diol, which formed hydrogen bonds with the PCz. As researchers slowly pulled the wafer out of the solution, the nanotubes self-assembled along the contact between the wafer and the butene diol, a process they named dimension-limited self-alignment.

Increasing the density of carbon nanotubes on the array is as simple as adding more of them to the solution, the researchers say.

Aaron Franklin, a chemist and electrical engineer at Duke University, says when he helped define the goals for the purity and density of carbon nanotubes 10 years ago, many people thought they couldn’t be met. “It really is a remarkable achievement,” he says. “The achievements in this work show a significant leap forward for high-performance CNT transistors.”

He worries that residue from the polymer might cause problems, an issue that Peng agrees needs to be addressed. Still, Peng is hopeful that chips containing carbon nanotubes could start to appear in the market within three to five years.

Nanotube transistors will allow new chip designs, including building 3-D architectures with dense interconnections that allow memory and processors to be packed close together, important for high-performance tasks like running artificial intelligence algorithms. This kind of stacking is not possible with silicon because the components are produced at such high temperatures that the interconnects would melt. Subhasish Mitra, an electrical engineer at Stanford University, thinks this and other work on nanotube-based circuits will lead to more of these architectures. “There are challenges, but they are surmountable challenges,” he says.

CORRECTION

This story was updated on May 21, 2020, to clarify how the researchers sorted the carbon nanotubes. They were not sorted by size.

Join the conversation

Contact the reporter

Submit a Letter to the Editor for publication

Engage with us on Twitter